The staggering compute requirements of generative models have transformed the modern data center into a high-stakes battlefield where the interconnect, rather than the chip itself, often determines the ultimate victor. As organizations scramble to scale their infrastructure, they find themselves tethered to proprietary ecosystems that prioritize vertical integration over industry-wide flexibility. The UALink Consortium has recently stepped into this fray by releasing the 2.0 specification, a bold attempt to provide an open-source alternative to the market-leading NVLink technology. This movement seeks to dismantle the “walled garden” approach that has defined high-performance computing for years, promising a future where disparate hardware can communicate with unprecedented efficiency.

The Evolution of the Interconnect Monopoly

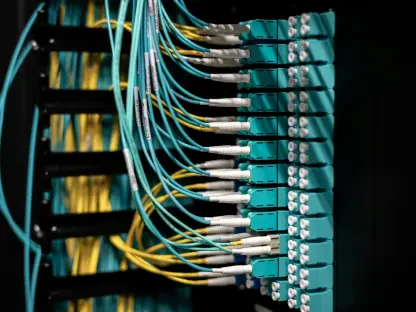

Historically, the efficiency of an artificial intelligence cluster was limited by the speed at which individual GPUs could exchange data. Nvidia addressed this bottleneck by moving away from standard PCIe lanes and introducing a proprietary fabric that allowed for massive scaling within its own hardware stacks. This strategy created a significant barrier to entry for competitors, as any enterprise wanting top-tier performance was essentially forced to remain within a single vendor’s ecosystem. While this led to rapid gains in training speeds, it also introduced substantial supply chain risks and cost pressures for cloud providers.

Previous industry efforts to standardize high-speed communication often lagged behind the sheer bandwidth and low-latency requirements of large-scale clusters. Consequently, the market evolved into a landscape dominated by a single gatekeeper, leaving hardware designers with few viable alternatives for multi-vendor integration. The lack of an open, high-performance fabric meant that even the most innovative startups had to optimize their silicon for existing proprietary paths or face obsolescence in the high-end data center market.

Engineering a Modular and Scalable Future

Decoupling Performance for Rapid Iteration

The most significant architectural shift in UALink 2.0 is the introduction of a decoupled “200G Data Link and Physical Layers Specification.” By separating the physical transport mechanisms from the core logic, the consortium has created a modular framework that allows manufacturers to iterate on hardware without redesigning the entire protocol stack. This flexibility is critical for keeping pace with the rapid advancements in silicon photonics and high-speed electrical signaling. It enables a more agile development cycle, where physical layer improvements—targeting speeds of 200Gbps per lane—can be integrated seamlessly into existing infrastructure designs.

In-Network Compute and Enhanced Manageability

To effectively compete with the specialized optimizations found in proprietary solutions, UALink 2.0 incorporates “In-Network Compute” capabilities. This technology allows the interconnect fabric to perform specific data processing tasks, such as reductions and aggregations, while the data is in transit between nodes. By offloading these tasks from the primary processors, the system significantly reduces round-trip latency and minimizes congestion in large-scale environments. Moreover, the standard now supports robust management protocols like Redfish and gNMI, ensuring that data center operators can monitor heterogeneous hardware through a single, unified interface.

Solving the Integration Puzzle with Chiplet Specs

The industry’s transition toward chiplet-based designs has necessitated a new approach to on-package communication, which UALink 2.0 addresses with a dedicated chiplet specification. This blueprint provides custom ASIC manufacturers with a standardized way to integrate high-speed interconnects directly into their Systems on Chip (SoCs). This is particularly attractive for companies building specialized AI accelerators that need to scale across multiple racks without being locked into a specific vendor’s license. However, a major hurdle remains the gap between theoretical specifications and physical production; until functional silicon reaches the assembly lines, the market remains reliant on established proprietary paths.

The Shifting Landscape of Data Center Connectivity

As we look toward the immediate future through 2028, the industry is approaching a pivot point where traditional copper-based wiring may no longer suffice for the distances required in massive AI clusters. Many leaders are already pivoting toward optical connectivity, which offers superior bandwidth and lower power consumption over longer distances. The UALink Consortium appears to be anticipating this shift, utilizing its rapid release cycle to signal that version 2.0 and its successors will eventually accommodate these physical transitions. This forward-looking stance is vital for maintaining relevance as the physical limitations of electrical signals become a hard ceiling for performance.

Beyond technical specifications, regulatory and geopolitical factors are beginning to favor open standards. The rise of sovereign AI initiatives—where nations seek to build independent technological foundations—creates a natural demand for vendor-neutral fabrics like UALink. If these regional projects choose to adopt open standards over proprietary ones, it could create the necessary volume to justify mass production of UALink-compliant hardware. Such a shift would not only diversify the supply chain but also force a more competitive pricing environment across the entire high-performance computing sector.

Strategic Realities for the AI Ecosystem

For hardware developers and enterprise architects, the arrival of UALink 2.0 demands a pragmatic evaluation of long-term infrastructure investments. While proprietary solutions currently provide the highest “out-of-the-box” performance, the risk of total vendor dependency is becoming increasingly difficult to ignore. Organizations should consider a dual-track strategy: utilizing current market leaders for immediate production needs while actively participating in UALink-ready pilot programs. Understanding the management protocols and in-network compute features of the new standard will be essential for those looking to manage the complex, multi-vendor environments that are likely to emerge in the coming years.

A Path Toward Open AI Infrastructure

The release of UALink 2.0 marked a sophisticated and necessary turning point in the effort to democratize data center connectivity. By prioritizing modularity, chiplet integration, and enterprise-level manageability, the consortium established a credible technical roadmap that challenged the prevailing proprietary status quo. The struggle for the future of the data center was no longer just about raw flops, but about the very architecture of communication between those units. The success of this initiative depended entirely on the speed at which hardware partners could move from published blueprints to functional products. Ultimately, the presence of UALink provided the industry with a vital insurance policy against the risks of a single-vendor future, ensuring that innovation remained driven by collective progress rather than closed-loop ecosystems.